What could possibly go wrong with <insert x86 instruction here>?

Clémentine Maurice, Moritz Lipp

December 2016—33rd Chaos Communication Congress

- · Clémentine Maurice

- PhD in computer science, Postdoc @ Graz University Of Technology

- ♥ @BloodyTangerine

- 🗹 clementine.maurice@iaik.tugraz.at

- Moritz Lipp

- PhD student @ Graz University Of Technology

- 🔰 @mlqxyz

- 🔽 moritz.lipp@iaik.tugraz.at

• title says this is a talk about x86 instructions but...

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- assuming "safe" software

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- assuming "safe" software

- does not mean safe execution

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- assuming "safe" software

- $\cdot$  does not mean safe execution

- information leaks because of the underlying hardware

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- assuming "safe" software

- does not mean safe execution

- information leaks because of the underlying hardware

- ightarrow cache attacks without memory accesses and bypassing kernel ASLR

- title says this is a talk about x86 instructions but...

- ... this is not a talk about software

- assuming "safe" software

- does not mean safe execution

- information leaks because of the underlying hardware

- ightarrow cache attacks without memory accesses and bypassing kernel ASLR

- $\rightarrow\,$  cache attacks can also be mounted on ARM, not solely on x86  $\,$

- Background

- $\cdot$  mov The beginning of cache attacks

- $\cdot$  clflush Cache attacks without memory accesses

- prefetch Lost in translation

- Bonus track Even more instructions, even more attacks

Introduction

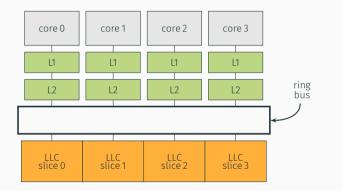

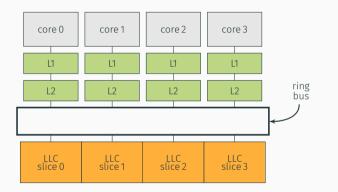

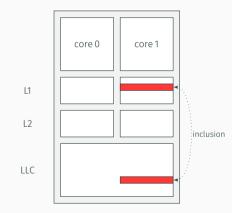

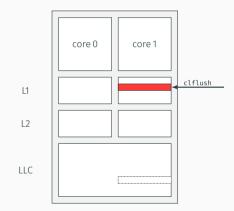

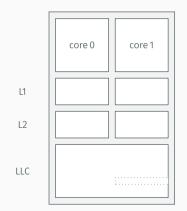

• L1 and L2 are private

- L1 and L2 are private

- last-level cache

- L1 and L2 are private

- last-level cache

- divided in slices

- L1 and L2 are private

- last-level cache

- $\cdot$  divided in slices

- shared across cores

- L1 and L2 are private

- last-level cache

- $\cdot$  divided in slices

- shared across cores

- inclusive

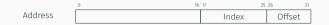

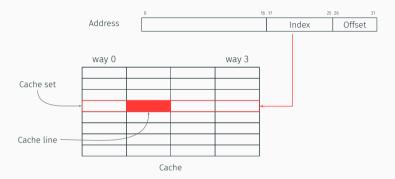

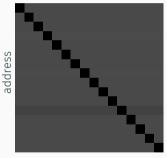

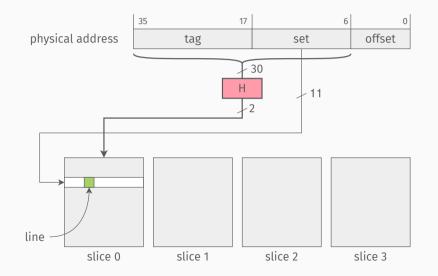

# Set-associative caches

Cache

Data loaded in a specific set depending on its address

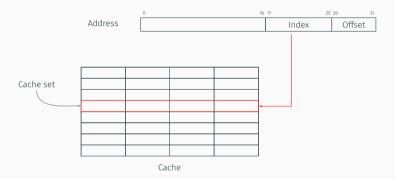

## Set-associative caches

Data loaded in a specific set depending on its address

Several ways per set

## Set-associative caches

Data loaded in a specific set depending on its address

Several ways per set

Cache line loaded in a specific way depending on the replacement policy

1. mov: accesses data in the main memory

- 1. mov: accesses data in the main memory

- 2. clflush: removes cache line from the cache

- 1. mov: accesses data in the main memory

- 2. clflush: removes cache line from the cache

- 3. prefetch: prefetches cache line for future use

- 1. mov: accesses data in the main memory

- 2. clflush: removes cache line from the cache

- 3. prefetch: prefetches cache line for future use

That's all the assembly you need for today!

#### mov

#### MOV-Move

| Opcode        | Instruction                                    | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                 |

|---------------|------------------------------------------------|-----------|----------------|---------------------|-------------------------------------------------------------|

| 88 /r         | MOV r/m8,r8                                    | MR        | Valid          | Valid               | Move r8 to r/m8.                                            |

| REX + 88 /r   | MOV <i>r/m8<sup>***,</sup>r8<sup>***</sup></i> | MR        | Valid          | N.E.                | Move <i>r8</i> to <i>r/m8.</i>                              |

| 89 /r         | MOV r/m16,r16                                  | MR        | Valid          | Valid               | Move <i>r16</i> to <i>r/m16.</i>                            |

| 89 /r         | MOV r/m32,r32                                  | MR        | Valid          | Valid               | Move <i>r32</i> to <i>r/m32.</i>                            |

| REX.W + 89 /r | MOV r/m64,r64                                  | MR        | Valid          | N.E.                | Move <i>r64</i> to <i>r/m64.</i>                            |

| 8A /r         | MOV <i>r8,r/m8</i>                             | RM        | Valid          | Valid               | Move r/m8 to r8.                                            |

| REX + 8A /r   | MOV r8***,r/m8***                              | RM        | Valid          | N.E.                | Move <i>r/m8</i> to <i>r8</i> .                             |

| 8B /r         | MOV r16,r/m16                                  | RM        | Valid          | Valid               | Move <i>r/m16</i> to <i>r16.</i>                            |

| 8B /r         | MOV <i>r32,r/m32</i>                           | RM        | Valid          | Valid               | Move <i>r/m32</i> to <i>r32.</i>                            |

| REX.W + 8B /r | MOV <i>r64,r/m64</i>                           | RM        | Valid          | N.E.                | Move <i>r/m64</i> to <i>r64.</i>                            |

| 8C /r         | MOV r/m16,Sreg**                               | MR        | Valid          | Valid               | Move segment register to r/m16.                             |

| REX.W + 8C /r | MOV r/m64,Sreg**                               | MR        | Valid          | Valid               | Move zero extended 16-bit segment register to <i>r/m64.</i> |

| 8E /r         | MOV Sreg,r/m16**                               | RM        | Valid          | Valid               | Move <i>r/m16</i> to segment register.                      |

| REX.W + 8E /r | MOV Sreg,r/m64**                               | RM        | Valid          | Valid               | Move <i>lower 16 bits of r/m64</i> to segment register.     |

| AO            | MOV AL, moffs 8*                               | FD        | Valid          | Valid               | Move byte at ( <i>seg:offset</i> ) to AL.                   |

| REX.W + A0    | MOV AL, moffs8*                                | FD        | Valid          | N.E.                | Move byte at (offset) to AL.                                |

| A1            | MOV AX,moffs16*                                | FD        | Valid          | Valid               | Move word at (seg:offset) to AX.                            |

| A1            | MOV EAX,moffs32*                               | FD        | Valid          | Valid               | Move doubleword at (seg:offset) to EAX.                     |

| REX.W + A1    | MOV RAX, moffs64*                              | FD        | Valid          | N.E.                | Move quadword at (offset) to RAX.                           |

| 64-Bit Mode Excep          | tions                                                                                                                                                                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #GP(0)                     | If the memory address is in a non-canonical form.                                                                                                                            |

|                            | If an attempt is made to load SS register with NULL segment selector when CPL = 3.                                                                                           |

|                            | If an attempt is made to load SS register with NULL segment selector when CPL < 3 and CPL $\neq$ RPL.                                                                        |

| #GP(selector)              | If segment selector index is outside descriptor table limits.                                                                                                                |

|                            | If the memory access to the descriptor table is non-canonical.                                                                                                               |

|                            | If the SS register is being loaded and the segment selector's RPL and the segment descriptor's DPL are not equal to the CPL.                                                 |

|                            | If the SS register is being loaded and the segment pointed to is a nonwritable data segment.                                                                                 |

|                            | If the DS, ES, FS, or GS register is being loaded and the segment pointed to is not a data or readable code segment.                                                         |

|                            | If the DS, ES, FS, or GS register is being loaded and the segment pointed to is a data or nonconforming code segment, but both the RPL and the CPL are greater than the DPL. |

| #SS(0)                     | If the stack address is in a non-canonical form.                                                                                                                             |

| #SS(selector)              | If the SS register is being loaded and the segment pointed to is marked not present.                                                                                         |

| <pre>#PF(fault-code)</pre> | If a page fault occurs.                                                                                                                                                      |

| #AC(0)                     | If alignment checking is enabled and an unaligned memory reference is made while the<br>current privilege level is 3.                                                        |

| #UD                        | If attempt is made to load the CS register.                                                                                                                                  |

|                            | If the LOCK prefix is used.                                                                                                                                                  |

$\cdot$  lots of exceptions for  $mo\nu$

- $\cdot$  lots of exceptions for  $mo\nu$

- $\cdot$  but accessing data loads it to the cache

- $\cdot$  lots of exceptions for  $mo\nu$

- $\cdot$  but accessing data loads it to the cache

- $\rightarrow$  side effects on computations!

• Data can reside in

- $\cdot$  Data can reside in

- CPU registers

- $\cdot$  Data can reside in

- CPU registers

- Different levels of the CPU cache

- $\cdot\,$  Data can reside in

- CPU registers

- Different levels of the CPU cache

- Main memory

- $\cdot\,$  Data can reside in

- CPU registers

- Different levels of the CPU cache

- Main memory

- Disk storage

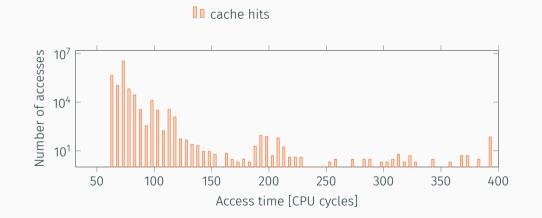

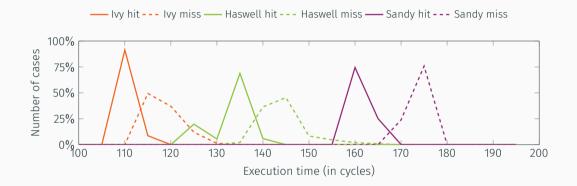

#### cache hits cache misses

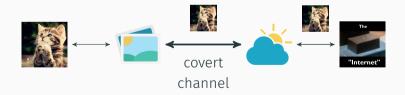

$\cdot\,$  cache attacks  $\rightarrow$  exploit timing differences of memory accesses

- $\cdot\,$  cache attacks  $\rightarrow$  exploit timing differences of memory accesses

- $\cdot$  attacker monitors which lines are accessed, not the content

- $\cdot\,$  cache attacks  $\rightarrow$  exploit timing differences of memory accesses

- $\cdot$  attacker monitors which lines are accessed, not the content

- covert channel: two processes communicating with each other

- not allowed to do so, e.g., across VMs

- $\cdot\,$  cache attacks  $\rightarrow$  exploit timing differences of memory accesses

- $\cdot$  attacker monitors which lines are accessed, not the content

- covert channel: two processes communicating with each other

- not allowed to do so, e.g., across VMs

- side-channel attack: one malicious process spies on benign processes

- e.g., steals crypto keys, spies on keystrokes

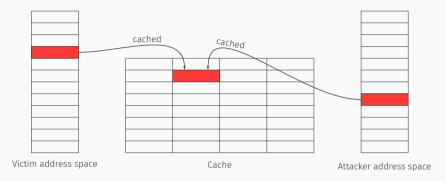

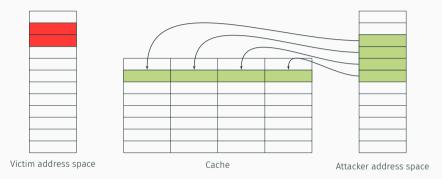

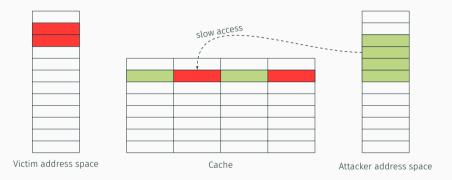

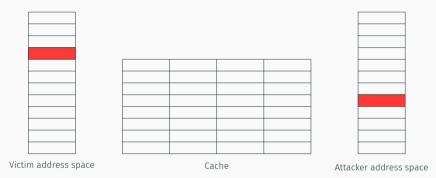

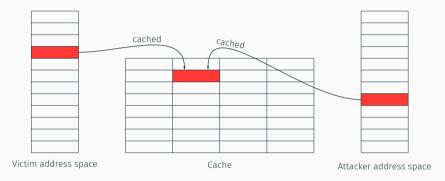

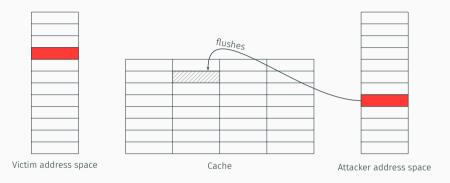

#### Step 1: Attacker maps shared library (shared memory, in cache)

Step 1: Attacker maps shared library (shared memory, in cache)

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 3: Victim loads the data

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 3: Victim loads the data

Step 4: Attacker reloads the data

| <br> | <br> |  |  |

|------|------|--|--|

|      |      |  |  |

|      |      |  |  |

|      |      |  |  |

|      |      |  |  |

| <br> | <br> |  |  |

|      |      |  |  |

|      |      |  |  |

| <br> | <br> |  |  |

|      |      |  |  |

|      |      |  |  |

|      |      |  |  |

Victim address space

Cache

Attacker address space

Step 1: Attacker primes, *i.e.*, fills, the cache (no shared memory)

Step 1: Attacker primes, *i.e.*, fills, the cache (no shared memory)

Step 2: Victim evicts cache lines while running

Step 1: Attacker primes, *i.e.*, fills, the cache (no shared memory)

Step 2: Victim evicts cache lines while running

Step 1: Attacker primes, *i.e.*, fills, the cache (no shared memory)

**Step 2:** Victim evicts cache lines while running

Step 3: Attacker probes data to determine if set has been accessed

Step 1: Attacker primes, *i.e.*, fills, the cache (no shared memory)

**Step 2:** Victim evicts cache lines while running

Step 3: Attacker probes data to determine if set has been accessed

• Malicious privacy gallery app

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious weather widget

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious weather widget

- No permissions except accessing the Internet

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious weather widget

- No permissions except accessing the Internet

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious weather widget

- No permissions except accessing the Internet

- Malicious privacy gallery app

- No permissions except accessing your images

- Malicious weather widget

- No permissions except accessing the Internet

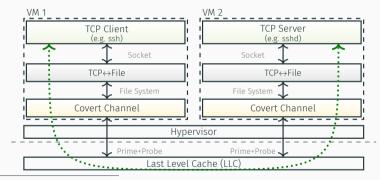

• sender and receiver agree on one set

- sender and receiver agree on one set

- receiver probes the set continuously

- $\cdot$  sender and receiver agree on one set

- receiver probes the set continuously

- sender transmits '0' doing nothing

- $\rightarrow~$  lines of the receiver still in cache  $\rightarrow~$  fast access

- $\cdot$  sender and receiver agree on one set

- receiver probes the set continuously

- sender transmits '0' doing nothing

- $\rightarrow~$  lines of the receiver still in cache  $\rightarrow~$  fast access

- $\cdot$  sender transmits '1' accessing addresses in the set

- $\rightarrow~{\rm evicts}$  lines of the receiver  $\rightarrow~{\rm slow}~{\rm access}$

- Prime+Probe: low requirements, works e.g., between VMs in Amazon EC2

- $\cdot$  error-free covert channel (40–75KBps)  $\rightarrow$  SSH connection over the cache

C. Maurice, M. Weber, M. Schwarz, L. Giner, D. Gruss, C. A. Boano, S. Mangard, and K. Römer. "Hello from the Other Side: SSH over Robust Cache Covert Channels in the Cloud". In: NDSS'17. to appear. 2017.

# Application #2 Crypto side-channel attack

• AES T-Tables: fast software implementation

- AES T-Tables: fast software implementation

- uses precomputed look-up tables

# Application #2: Crypto side-channel attack

- AES T-Tables: fast software implementation

- uses precomputed look-up tables

- one-round known-plaintext attack by Osvik et al. (2006)

- *p* plaintext and *k* secret key

- intermediate state  $x^{(r)} = (x_0^{(r)}, \dots, x_{15}^{(r)})$  at each round r

- first round, accessed table indices are

$$x_i^{(0)} = p_i \oplus k_i$$

for all  $i = 0, \dots, 15$

# Application #2: Crypto side-channel attack

- AES T-Tables: fast software implementation

- uses precomputed look-up tables

- one-round known-plaintext attack by Osvik et al. (2006)

- *p* plaintext and *k* secret key

- intermediate state  $x^{(r)} = (x_0^{(r)}, \dots, x_{15}^{(r)})$  at each round r

- first round, accessed table indices are

$$x_i^{(0)} = p_i \oplus k_i$$

for all  $i = 0, \dots, 15$

$\rightarrow\,$  recovering accessed table indices  $\Rightarrow\,$  recovering the key

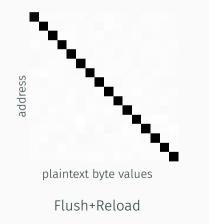

### Application #2: Crypto side-channel attack

• monitoring which T-Table entry is accessed ( $k_0 = 0 \times 00$ )

plaintext byte values

Prime+Probe

• it's an old attack...

- it's an old attack...

- everything should be fixed by now...

- it's an old attack...

- everything should be fixed by now...

- $\cdot\,$  Bouncy Castle on Android  $\rightarrow$  default implementation uses T-Tables

- many implementations you find online use pre-computed values

Application #3 Spying on keystrokes • Flush+Reload: fine-grained attack  $\rightarrow$  spy on keystrokes

M. Lipp, D. Gruss, R. Spreitzer, C. Maurice, and S. Mangard. "ARMageddon: Cache Attacks on Mobile Devices". In: USENIX Security Symposium. 2016

• Flush+Reload: fine-grained attack  $\rightarrow$  spy on keystrokes

# Demo time!

M. Lipp, D. Gruss, R. Spreitzer, C. Maurice, and S. Mangard. "ARMageddon: Cache Attacks on Mobile Devices". In: USENIX Security Symposium. 2016

## clflush

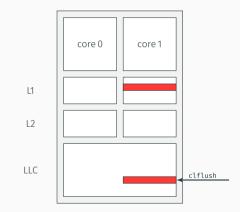

• clflush: invalidates from every level the cache line containing the address

- clflush: invalidates from every level the cache line containing the address

- in itself enables Flush+Reload attacks

- clflush: invalidates from every level the cache line containing the address

- in itself enables Flush+Reload attacks

- but there's more!

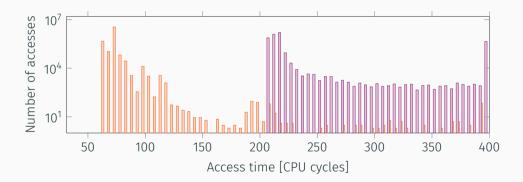

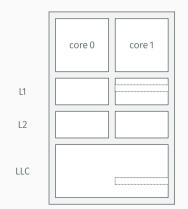

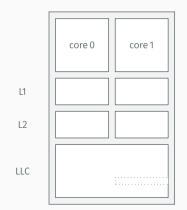

• clflush on cached data

- clflush on cached data

- goes to LLC, flushes line

- clflush on cached data

- goes to LLC, flushes line

### clflush timing leakage: Part #1

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- $\cdot$  goes to LLC, does nothing

- clflush on cached data

- goes to LLC, flushes line

- flushes line in L1-L2

- $\rightarrow$  slow

- clflush on non-cached data

- $\cdot$  goes to LLC, does nothing

- $\rightarrow$  fast

D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

- new cache attack: Flush+Flush

- · covert channels and side-channel attacks

D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

- new cache attack: Flush+Flush

- covert channels and side-channel attacks

- stealthier than previous cache attacks

D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

- new cache attack: Flush+Flush

- covert channels and side-channel attacks

- stealthier than previous cache attacks

- faster than previous cache attacks

D. Gruss, C. Maurice, K. Wagner, and S. Mangard. "Flush+Flush: A Fast and Stealthy Cache Attack". In: DIMVA'16. 2016.

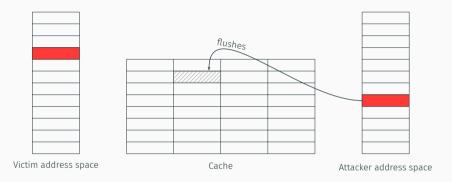

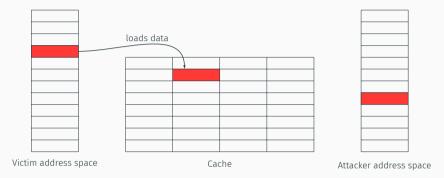

#### Step 1: Attacker maps shared library (shared memory, in cache)

Step 1: Attacker maps shared library (shared memory, in cache)

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 3: Victim loads the data

Step 1: Attacker maps shared library (shared memory, in cache)

Step 2: Attacker flushes the shared cache line

Step 3: Victim loads the data

Step 4: Attacker flushes the data

- 1. CACHE\_MISSES  $\rightarrow$  occur after data is flushed

- 2. CACHE\_REFERENCES  $\rightarrow$  occur when reaccessing memory

N. Herath and A. Fogh. "These are Not Your Grand Daddys CPU Performance Counters – CPU Hardware Performance Counters for Security". In: Black Hat 2015 Briefings. 2015

- 1. CACHE\_MISSES  $\rightarrow$  occur after data is flushed

- 2. CACHE\_REFERENCES  $\rightarrow$  occur when reaccessing memory

... without false positives

N. Herath and A. Fogh. "These are Not Your Grand Daddys CPU Performance Counters – CPU Hardware Performance Counters for Security". In: Black Hat 2015 Briefings. 2015

- 1. CACHE\_MISSES  $\rightarrow$  occur after data is flushed

- 2. CACHE\_REFERENCES  $\rightarrow$  occur when reaccessing memory

... without false positives

heavy activity on the cache

N. Herath and A. Fogh. "These are Not Your Grand Daddys CPU Performance Counters – CPU Hardware Performance Counters for Security". In: Black Hat 2015 Briefings. 2015

- 1. CACHE\_MISSES  $\rightarrow$  occur after data is flushed

- 2. CACHE\_REFERENCES  $\rightarrow$  occur when reaccessing memory

... without false positives

- heavy activity on the cache

- $\cdot\,$  also, very short loops of code  $\rightarrow$  low pressure on the iTLB

N. Herath and A. Fogh. "These are Not Your Grand Daddys CPU Performance Counters – CPU Hardware Performance Counters for Security". In: Black Hat 2015 Briefings. 2015

- 1. CACHE\_MISSES  $\rightarrow$  occur after data is flushed

- 2. CACHE\_REFERENCES  $\rightarrow$  occur when reaccessing memory

... without false positives

- heavy activity on the cache

- $\cdot\,$  also, very short loops of code  $\rightarrow$  low pressure on the iTLB

- $\rightarrow$  normalize the events by ITLB\_RA+ITLB\_RM

N. Herath and A. Fogh. "These are Not Your Grand Daddys CPU Performance Counters – CPU Hardware Performance Counters for Security". In: Black Hat 2015 Briefings. 2015

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          |                    |                     |                   |

| Flush+Reload | 28          |                    |                     |                   |

|              |             |                    |                     |                   |

| technique                   | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |  |

|-----------------------------|-------------|--------------------|---------------------|-------------------|--|

| Flush+Flush<br>Flush+Reload | 28<br>28    | 496<br>298         |                     |                   |  |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | √                   |                   |

| Flush+Reload | 28          | 298                | ×                   |                   |

| technique                   | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |  |

|-----------------------------|-------------|--------------------|---------------------|-------------------|--|

| Flush+Flush<br>Flush+Reload | 28<br>28    | 496<br>298         | ×                   | X<br>X            |  |

| technique                | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |  |

|--------------------------|-------------|--------------------|---------------------|-------------------|--|

| <mark>Flush+Flush</mark> | 28          | 496                | √                   | ×                 |  |

| Flush+Reload             | 28          | 298                | ×                   | ×                 |  |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | 1                   | ×                 |

| Flush+Reload | 28          | 298                | ×                   | ×                 |

| Flush+Reload | 4           |                    |                     |                   |

| Flush+Flush  | 4           |                    |                     |                   |

| Prime+Probe  | 4           |                    |                     |                   |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | 1                   | ×                 |

| Flush+Reload | 28          | 298                | ×                   | ×                 |

| Flush+Reload | 4           | 54                 |                     |                   |

| Flush+Flush  | 4           | 52                 |                     |                   |

| Prime+Probe  | 4           | 34                 |                     |                   |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | 1                   | ×                 |

| Flush+Reload | 28          | 298                | ×                   | ×                 |

| Flush+Reload | 4           | 54                 | ×                   |                   |

| Flush+Flush  | 4           | 52                 | $\checkmark$        |                   |

| Prime+Probe  | 4           | 34                 | ×                   |                   |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | 1                   | ×                 |

| Flush+Reload | 28          | 298                | ×                   | ×                 |

| Flush+Reload | 4           | 54                 | ×                   | $\checkmark$      |

| Flush+Flush  | 4           | 52                 | $\checkmark$        | $\checkmark$      |

| Prime+Probe  | 4           | 34                 | ×                   | ×                 |

| technique    | packet size | capacity<br>(KBps) | receiver<br>stealth | sender<br>stealth |

|--------------|-------------|--------------------|---------------------|-------------------|

| Flush+Flush  | 28          | 496                | 1                   | ×                 |

| Flush+Reload | 28          | 298                | ×                   | ×                 |

| Flush+Reload | 4           | 54                 | ×                   | $\checkmark$      |

| Flush+Flush  | 4           | 52                 | $\checkmark$        | $\checkmark$      |

| Prime+Probe  | 4           | 34                 | ×                   | ×                 |

#### Number of encryptions to determine the upper 4 bits of a key byte

| technique    | number of encryptions |

|--------------|-----------------------|

| Flush+Reload | 250                   |

| Flush+Flush  | 350                   |

| Prime+Probe  | 4 800                 |

$\rightarrow$  same performance for Flush+Flush and Flush+Reload

Stealthiness comparison on 256 million encryptions (synchronous attack)

| technique    | time (s) | stealth      |

|--------------|----------|--------------|

| Flush+Reload | 215      | ×            |

| Prime+Probe  | 234      | ×            |

| Flush+Flush  | 163      | $\checkmark$ |

$\rightarrow$  Flush+Flush is the only stealth spy process

ightarrow others need to be slowed down too much to be practical

A little bit more background before continuing...

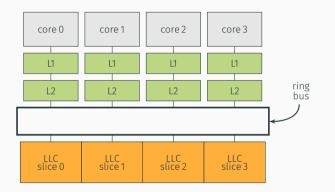

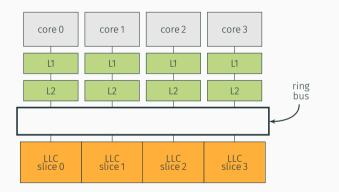

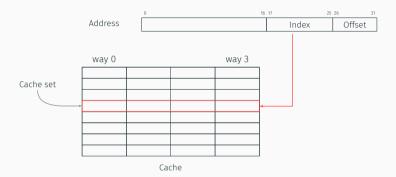

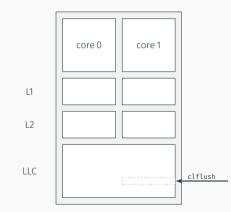

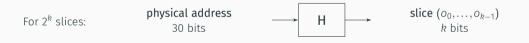

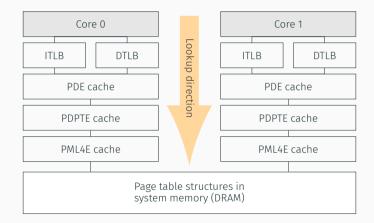

## Last-level cache (1)

- $\cdot\,$  last-level cache  $\rightarrow$  as many slices as cores

- undocumented hash function that maps a physical address to a slice

- designed for performance

# Let's go back to clflush!

### clflush timing leakage: Part #2

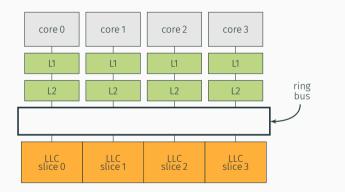

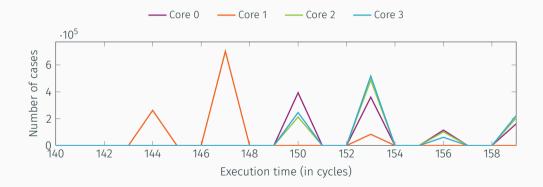

• clflush faster to reach a line on the local slice

#### clflush timing leakage: Part #2

• clflush faster to reach a line on the local slice

• map physical addresses to slices

- map physical addresses to slices

- one way to reverse-engineer the addressing function

- map physical addresses to slices

- one way to reverse-engineer the addressing function

- other way: using performance counters<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> C. Maurice, N. Le Scouarnec, C. Neumann, O. Heen, and A. Francillon. "Reverse Engineering Intel Complex Addressing Using Performance Counters". In: *RAID'15*. 2015

# prefetch

prefetch fetches the line of data from memory containing the specified byte

6 **prefetch** instructions:

- prefetcht0: suggests CPU to load data into L1

- prefetcht1: suggests CPU to load data into L2

- prefetcht2: suggests CPU to load data into L3

- prefetchnta: suggests CPU to load data for non-temporal access

- prefetchw: suggests CPU to load data with intention to write

- prefetchwt1: suggests CPU to load vector data with intention to write

#### prefetch according to Intel

#### NOTE

Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. 2014

Using the PREFETCH instruction is recommended only if data does not fit in cache.

Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. 2014

Using the PREFETCH instruction is recommended only if data does not fit in cache. Use of software prefetch should be limited to memory addresses that are managed or owned within the application context.

Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. 2014

Using the PREFETCH instruction is recommended only if data does not fit in cache. Use of software prefetch should be limited to memory addresses that are managed or owned within the application context. Prefetching to addresses that are **not mapped** to physical pages can experience **non-deterministic** performance penalty.

Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. 2014

Using the PREFETCH instruction is recommended only if data does not fit in cache. Use of software prefetch should be limited to memory addresses that are managed or owned within the application context. Prefetching to addresses that are **not mapped** to physical pages can experience **non-deterministic** performance penalty. For example specifying a NULL pointer (OL) as address for a prefetch can cause **long delays**.

Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. 2014

A little bit more background before continuing...

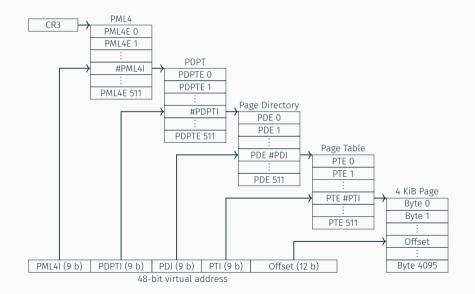

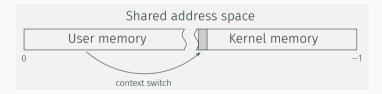

#### Address translation caches

#### Today's operating systems:

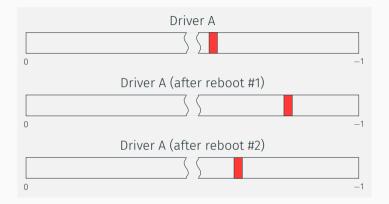

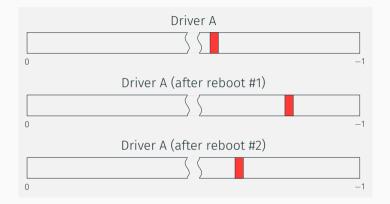

#### Kernel Address Space Layout Randomization (KASLR)

• same driver, different offset at each boot

### Kernel Address Space Layout Randomization (KASLR)

- same driver, different offset at each boot

- leaking kernel/driver addresses defeats KASLR

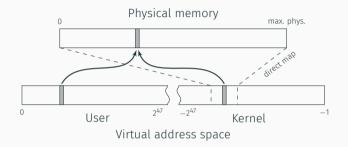

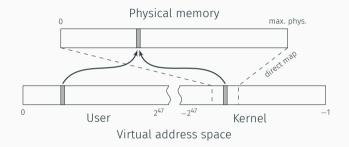

## Kernel direct-physical map

• OS X, Linux, BSD, Xen PVM (Amazon EC2)

## Kernel direct-physical map

- OS X, Linux, BSD, Xen PVM (Amazon EC2)

- not Windows

# Let's go back to prefetch!

• tells the CPU "I might need that later"

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

- tells the CPU "I might need that later"

- hint—may be ignored by the CPU

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

- tells the CPU "I might need that later"

- $\cdot$  hint—may be ignored by the CPU

- generates no faults

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

- tells the CPU "I might need that later"

- hint—may be ignored by the CPU

- generates no faults

Property #1: do not check privileges

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

• operand is a virtual address

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

- operand is a virtual address

- but it needs to translate the virtual address to a physical address

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

- operand is a virtual address

- but it needs to translate the virtual address to a physical address

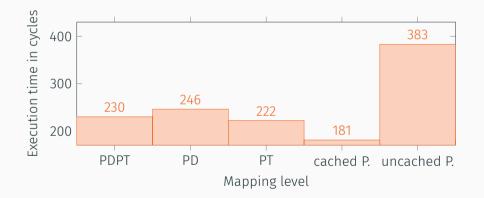

Property #2: execution time varies

D. Gruss, C. Maurice, A. Fogh, M. Lipp, and S. Mangard. "Prefetch Side-Channel Attacks: Bypassing SMAP and Kernel ASLR". . In: CCS'16. 2016

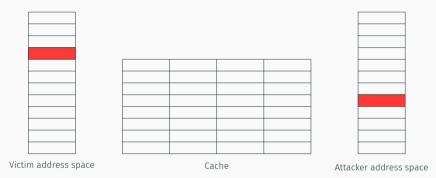

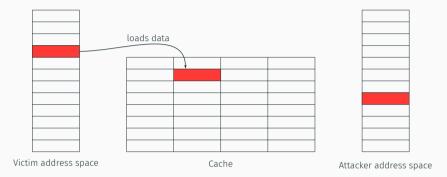

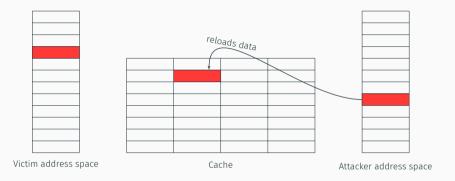

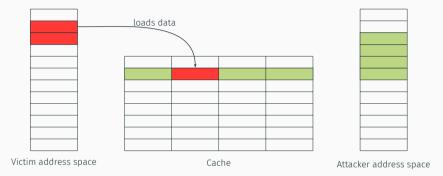

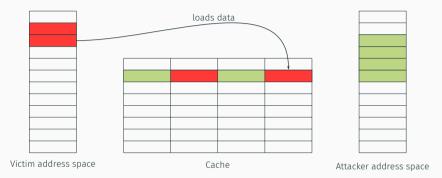

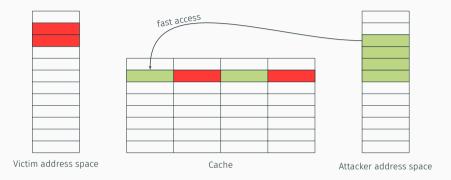

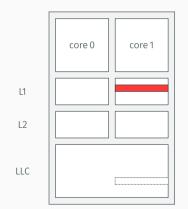

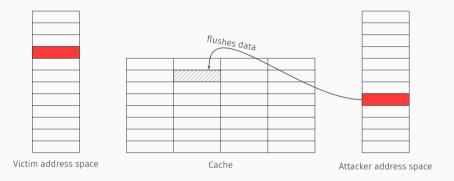

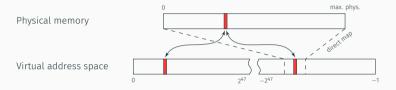

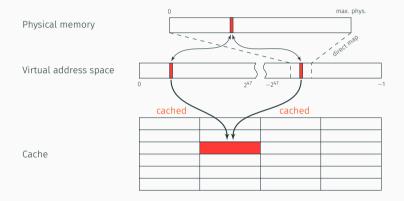

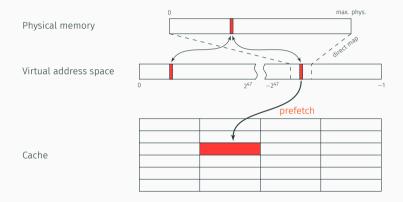

#### Exploiting property #1 + kernel direct-physical map

Cache

#### Exploiting property #1 + kernel direct-physical map

#### Exploiting property #1 + kernel direct-physical map

#### Exploiting property #1 + kernel direct-physical map

Exploiting property #1 + kernel direct-physical map

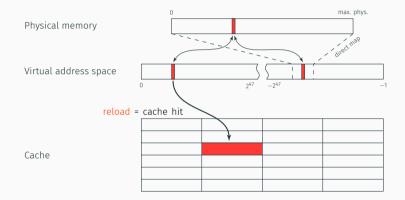

$\cdot\,$  cache hit  $\rightarrow$  physical address in kernel mapping is the correct translation

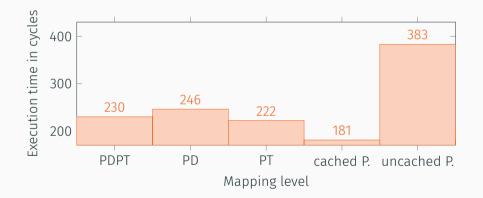

Exploiting property #2

Exploiting property #2

• timing depends on where the translation stops

• variants of cache attacks (e.g., Flush+Prefetch)

- variants of cache attacks (e.g., Flush+Prefetch)

- Rowhammer attacks on privileged addresses

- variants of cache attacks (e.g., Flush+Prefetch)

- Rowhammer attacks on privileged addresses

- recovering translation levels of a process ( $\rightarrow$  /proc/pid/pagemap)

- $\rightarrow~\text{now privileged} \rightarrow \text{bypasses}~\text{ASLR}$

- variants of cache attacks (e.g., Flush+Prefetch)

- Rowhammer attacks on privileged addresses

- recovering translation levels of a process ( $\rightarrow$  /proc/pid/pagemap)

- $\rightarrow~\text{now privileged} \rightarrow \text{bypasses}~\text{ASLR}$

- translating virtual addresses to physical addresses ( $\rightarrow \texttt{/proc/pid/pagemap})$

- $\rightarrow \mbox{ now privileged } \rightarrow \mbox{ re-enables ret2dir exploits}$

- variants of cache attacks (e.g., Flush+Prefetch)

- Rowhammer attacks on privileged addresses

- · recovering translation levels of a process ( $\rightarrow$  /proc/pid/pagemap)

- $\rightarrow$  now privileged  $\rightarrow$  bypasses ASLR

- translating virtual addresses to physical addresses ( $\rightarrow$  /proc/pid/pagemap)  $\rightarrow$  now privileged  $\rightarrow$  re-enables ret2dir exploits

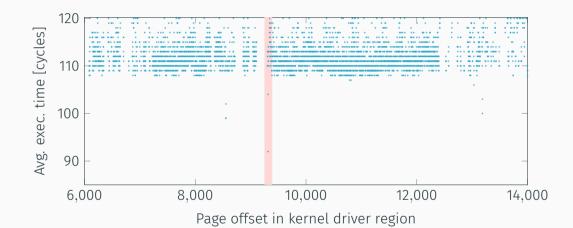

- locating kernel drivers

- $\rightarrow$  bypasses KASLR

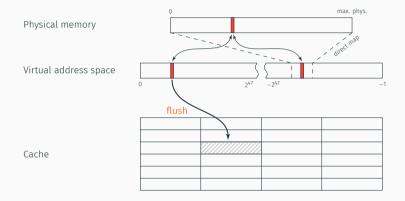

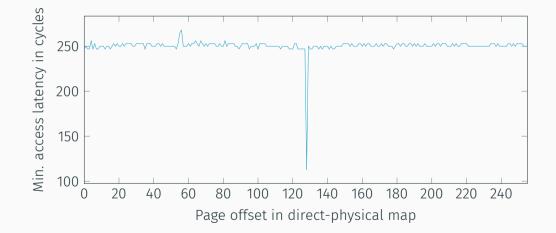

1. evict translation caches: Sleep() / access large memory buffer

- 1. evict translation caches: Sleep() / access large memory buffer

- 2. perform syscall to driver

- 1. evict translation caches: Sleep() / access large memory buffer

- 2. perform syscall to driver

- 3. time prefetch(page address)

- 1. evict translation caches: Sleep() / access large memory buffer

- 2. perform syscall to driver

- 3. time prefetch(page address)

- $\rightarrow\,$  fastest average access time is a driver page

- 1. evict translation caches: Sleep() / access large memory buffer

- 2. perform syscall to driver

- 3. time prefetch(page address)

- $\rightarrow\,$  fastest average access time is a driver page

Full attack on Windows 10 in < 12 seconds

## Defeating KASLR by locating kernel driver (2)

# That's not all folks!

## $\cdot$ rdseed

- request a random seed to the hardware random number generator

- $\cdot$  fixed number of precomputed random bits, takes time to regenerate them

- $\rightarrow$  covert channel

D. Evtyushkin and D. Ponomarev. "Covert Channels through Random Number Generator: Mechanisms, Capacity Estimation and Mitigations". In: CCS'16. 2016

M. Andrysco, D. Kohlbrenner, K. Mowery, R. Jhala, S. Lerner, and H. Shacham. "On subnormal floating point and abnormal timing". In: S&P'15. 2015

## $\cdot$ rdseed

- request a random seed to the hardware random number generator

- $\cdot\,$  fixed number of precomputed random bits, takes time to regenerate them

- $\rightarrow$  covert channel

- $\cdot$  fadd,fmul

- floating point operations

- running time depends on the operands

- $\rightarrow\,$  bypassing Firefox's same origin policy via SVG filter timing attack

D. Evtyushkin and D. Ponomarev. "Covert Channels through Random Number Generator: Mechanisms, Capacity Estimation and Mitigations". In: CCS'16. 2016

M. Andrysco, D. Kohlbrenner, K. Mowery, R. Jhala, S. Lerner, and H. Shacham. "On subnormal floating point and abnormal timing". In: S&P'15. 2015

## • jmp

- branch prediction and branch target prediction

- ightarrow covert channels, side-channel attacks on crypto, bypassing kernel ASLR

O. Acliçmez, J.-P. Seifert, and c. K. Koç. "Predicting secret keys via branch prediction". In: *CT-RSA 2007*. 2007 D. Evtyushkin, D. Ponomarev, and N. Abu-Ghazaleh. "Jump over ASLR: Attacking branch predictors to bypass ASLR". In: *MICRO'16*. 2016 Y. Jang, S. Lee, and T. Kim. "Breaking kernel address space layout randomization with intel TSX". In: *CCS'16*. 2016

# · jmp

- $\cdot$  branch prediction and branch target prediction

- $\rightarrow~{\rm covert}$  channels, side-channel attacks on crypto, bypassing kernel ASLR

- TSX instructions

- $\cdot$  extension for hardware transactional memory support

- ightarrow bypassing kernel ASLR

O. Acliçmez, J.-P. Seifert, and c. K. Koç. "Predicting secret keys via branch prediction". In: CT-RSA 2007. 2007 D. Evtyushkin, D. Ponomarev, and N. Abu-Ghazaleh. "Jump over ASLR: Attacking branch predictors to bypass ASLR". In: MICRO'16. 2016 Y. Jang, S. Lee, and T. Kim. "Breaking kernel address space layout randomization with intel TSX". In: CCS'16. 2016

Conclusion

• more a problem of CPU design than Instruction Set Architecture

- more a problem of CPU design than Instruction Set Architecture

- $\cdot\,$  hard to patch  $\rightarrow$  issues linked to performance optimizations

- more a problem of CPU design than Instruction Set Architecture

- $\cdot\,$  hard to patch  $\rightarrow$  issues linked to performance optimizations

- quick fixes like removing instructions won't work

- more a problem of CPU design than Instruction Set Architecture

- $\cdot\,$  hard to patch  $\rightarrow$  issues linked to performance optimizations

- quick fixes like removing instructions won't work

- $\rightarrow\,$  we keep finding new instructions that leak information

What could possibly go wrong with <insert x86 instruction here>?

Clémentine Maurice, Moritz Lipp

December 2016—33rd Chaos Communication Congress